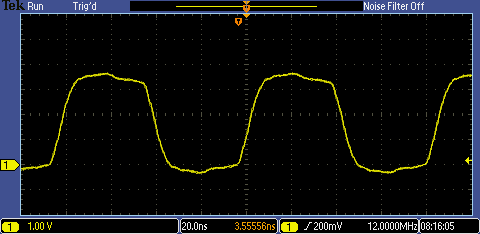

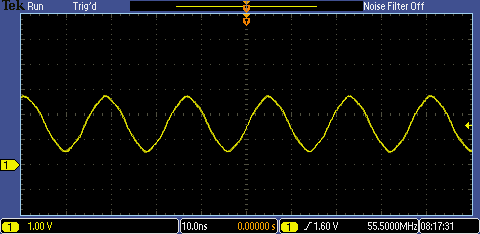

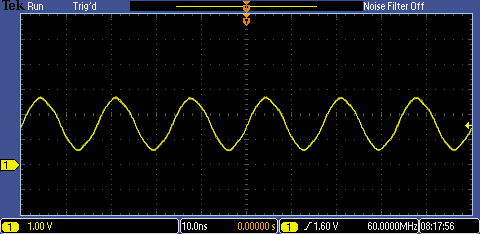

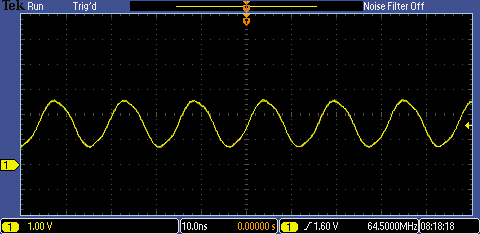

# iCE40 Ring Test ## Dependencies - [IceStorm tools](https://github.com/YosysHQ/icestorm) - [yosys](http://www.clifford.at/yosys/download.html) - [nextpnr](https://github.com/YosysHQ/nextpnr) Install instructions for all of the above tools can be found on the [IceStorm website](http://bygone.clairexen.net/icestorm/). ## Building The default `make` target synthesizes the design and runs a timing analysis. The target `prog` programs an available iCEBreaker via USB. ## Results When clocking the FPGA at 24MHz, the resulting ring oscillation is still identifiable as a square wave.  By 111MHz, it's more of a triangle wave. But still stable and nearly rail to rail. This is the fastest clock speed that `icetime` approves.  Despite not passing the timing analysis, when the FPGA is clocked at 120MHz no problems seems to occur.  Even at 129MHz, stable ring oscillation can occur. I (Erik) thought that the first time I ran it I got a chaotic, aperiodic signal. But I haven't been able to reproduce this so I might have made a mistake. Still, I'll hold off on declaring this result official.  At faster clock speeds things start to go wrong. Usually there's still a periodic ring oscillation, just much slower than one would hope.