added test board for as5013 ic

Showing

- as5013-test/as5013-test-interior.png 0 additions, 0 deletionsas5013-test/as5013-test-interior.png

- as5013-test/as5013-test-layout.png 0 additions, 0 deletionsas5013-test/as5013-test-layout.png

- as5013-test/as5013-test-traces.png 0 additions, 0 deletionsas5013-test/as5013-test-traces.png

- as5013-test/as5013-test.ko 290 additions, 0 deletionsas5013-test/as5013-test.ko

as5013-test/as5013-test-interior.png

0 → 100644

19.2 KiB

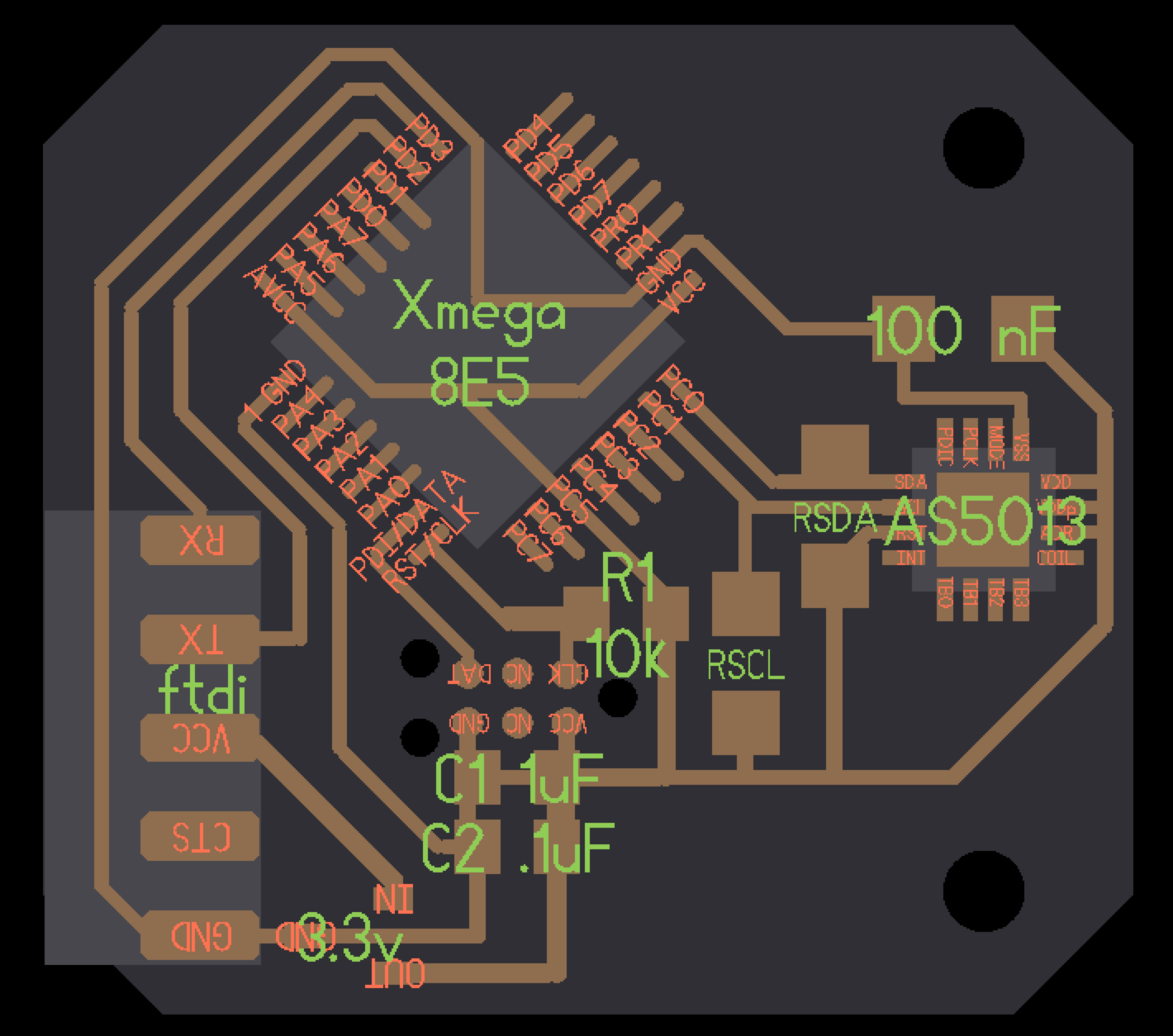

as5013-test/as5013-test-layout.png

0 → 100644

212 KiB

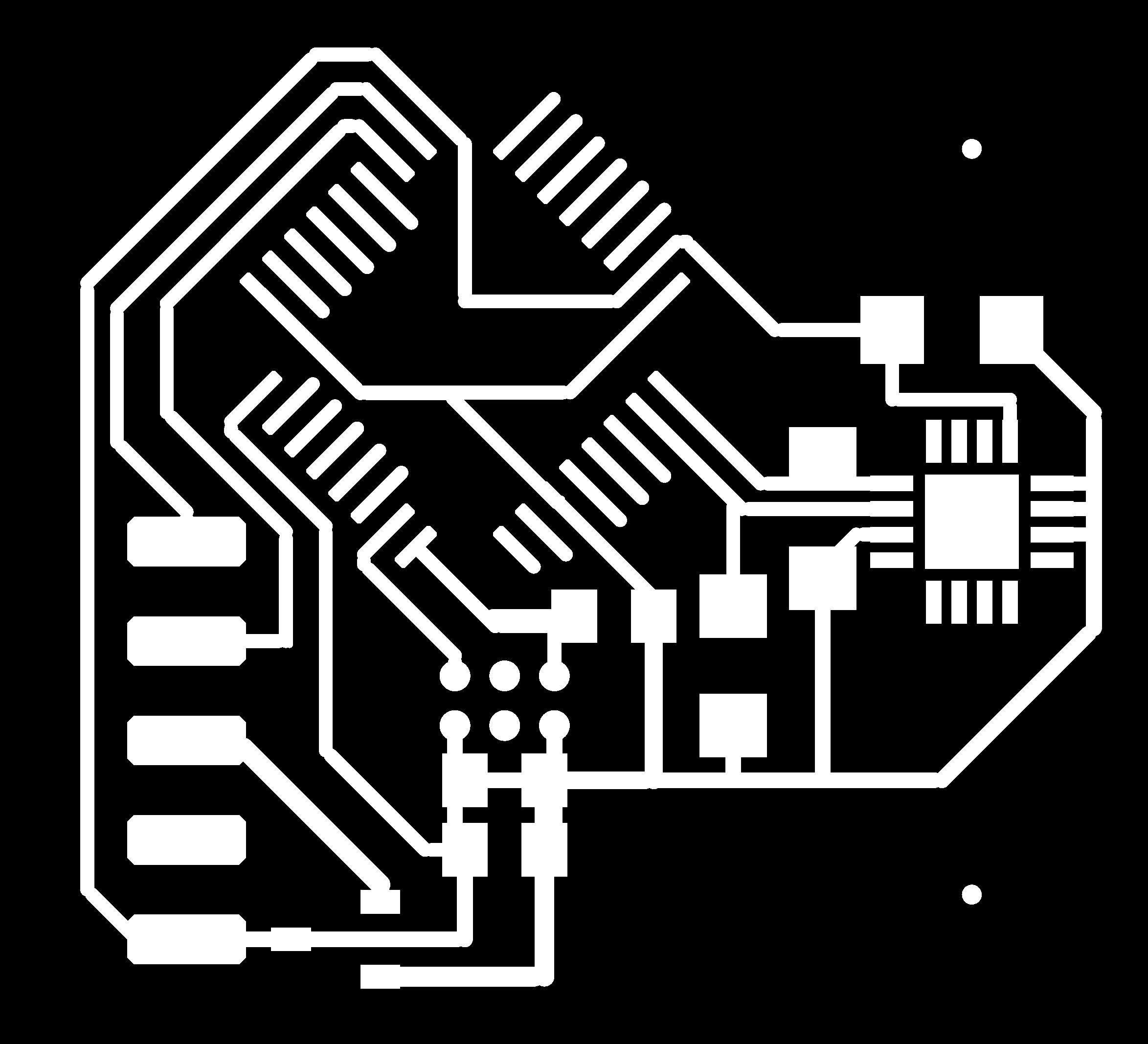

as5013-test/as5013-test-traces.png

0 → 100644

43 KiB

as5013-test/as5013-test.ko

0 → 100644