-

- Downloads

There was a problem fetching the pipeline summary.

fix reset line

parent

7dc0327b

No related branches found

No related tags found

Pipeline #

Showing

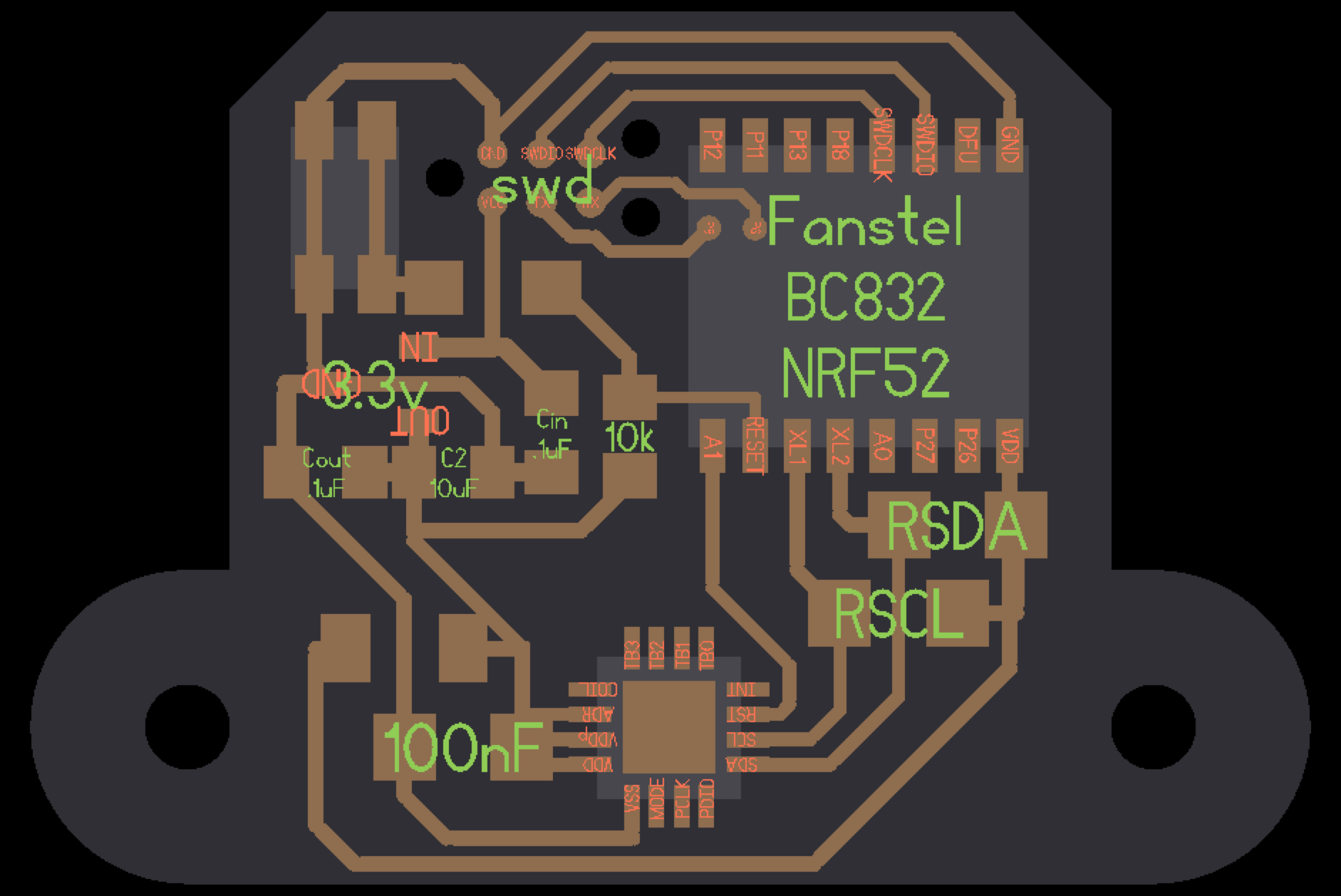

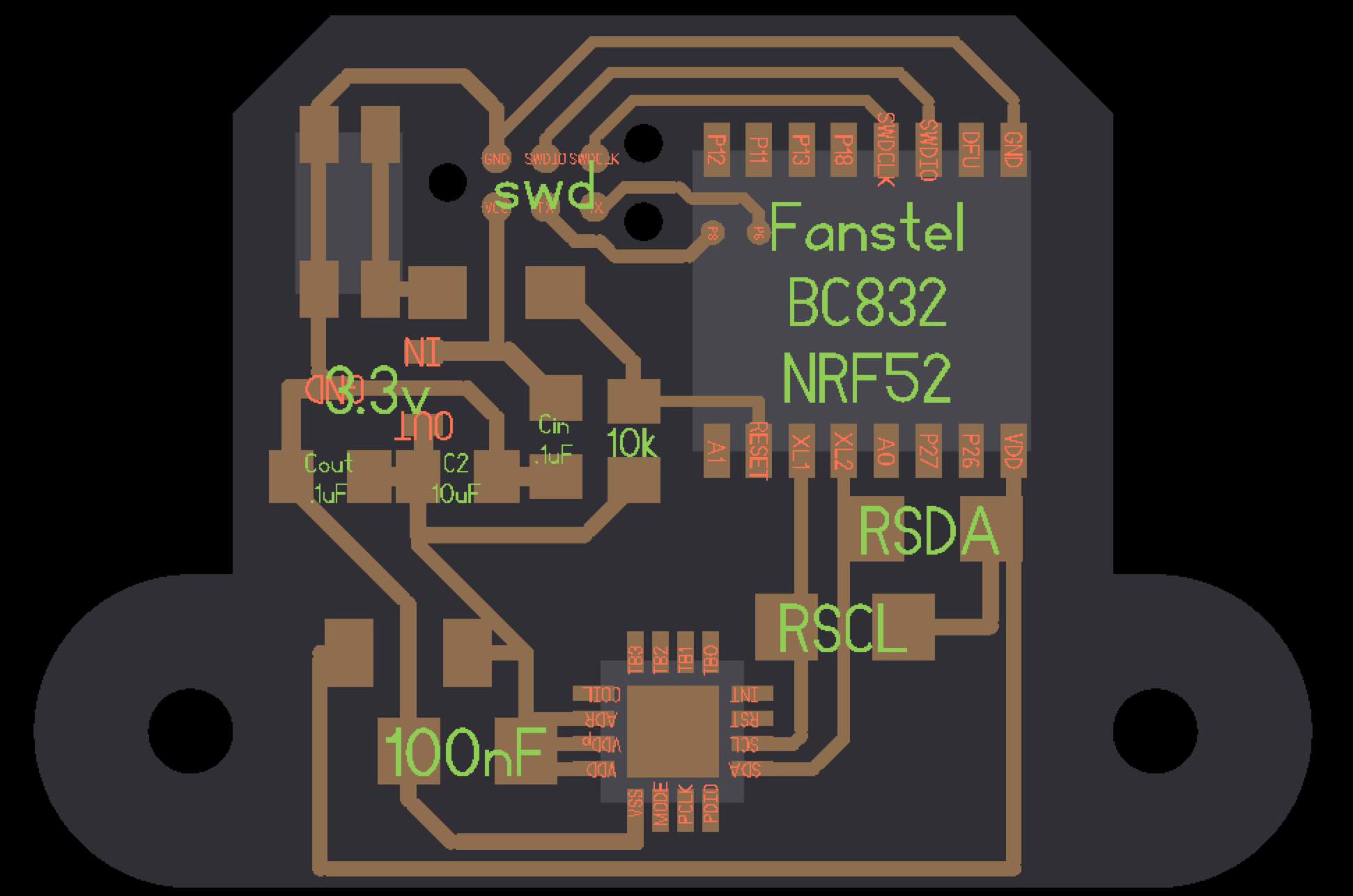

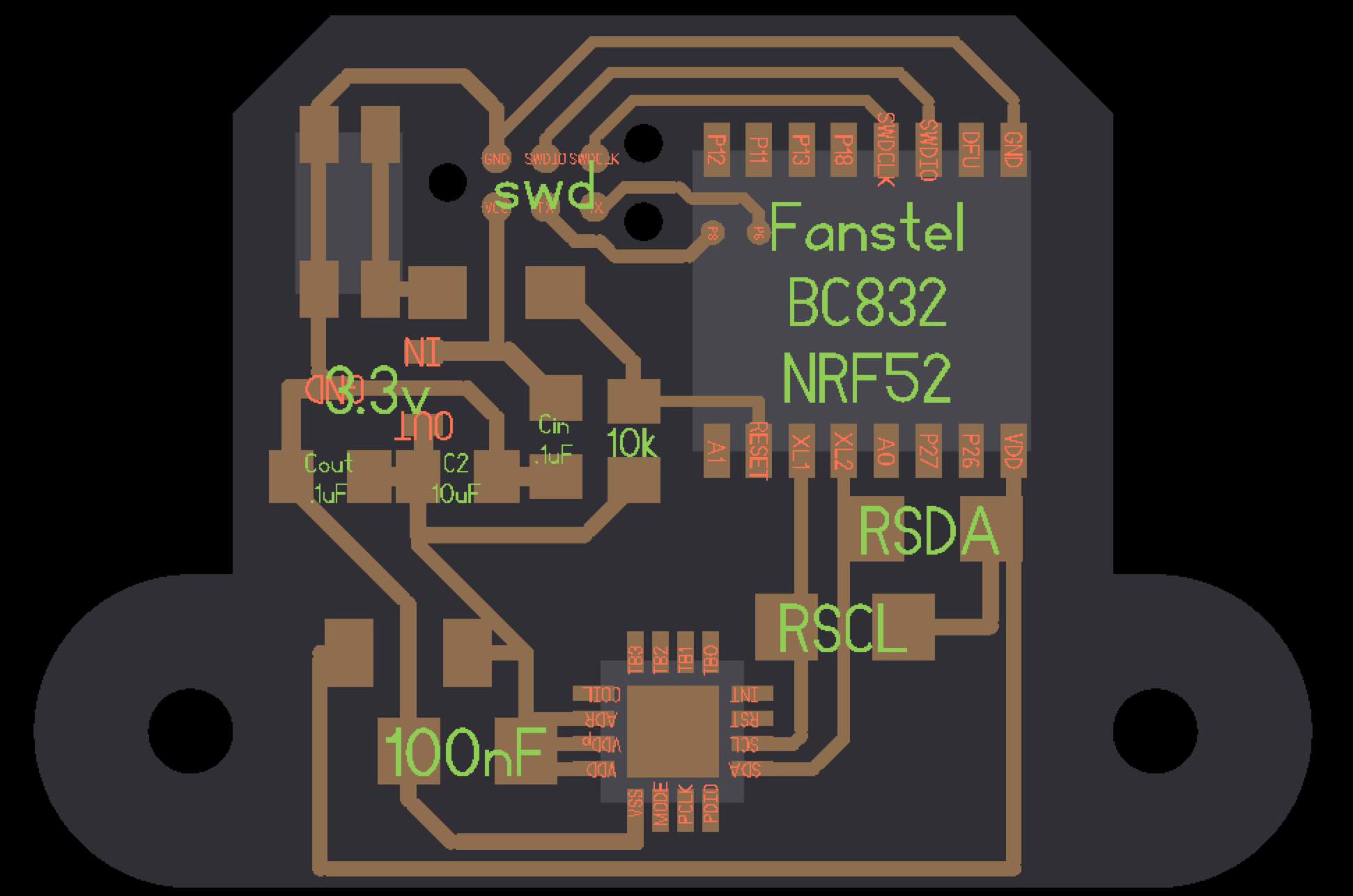

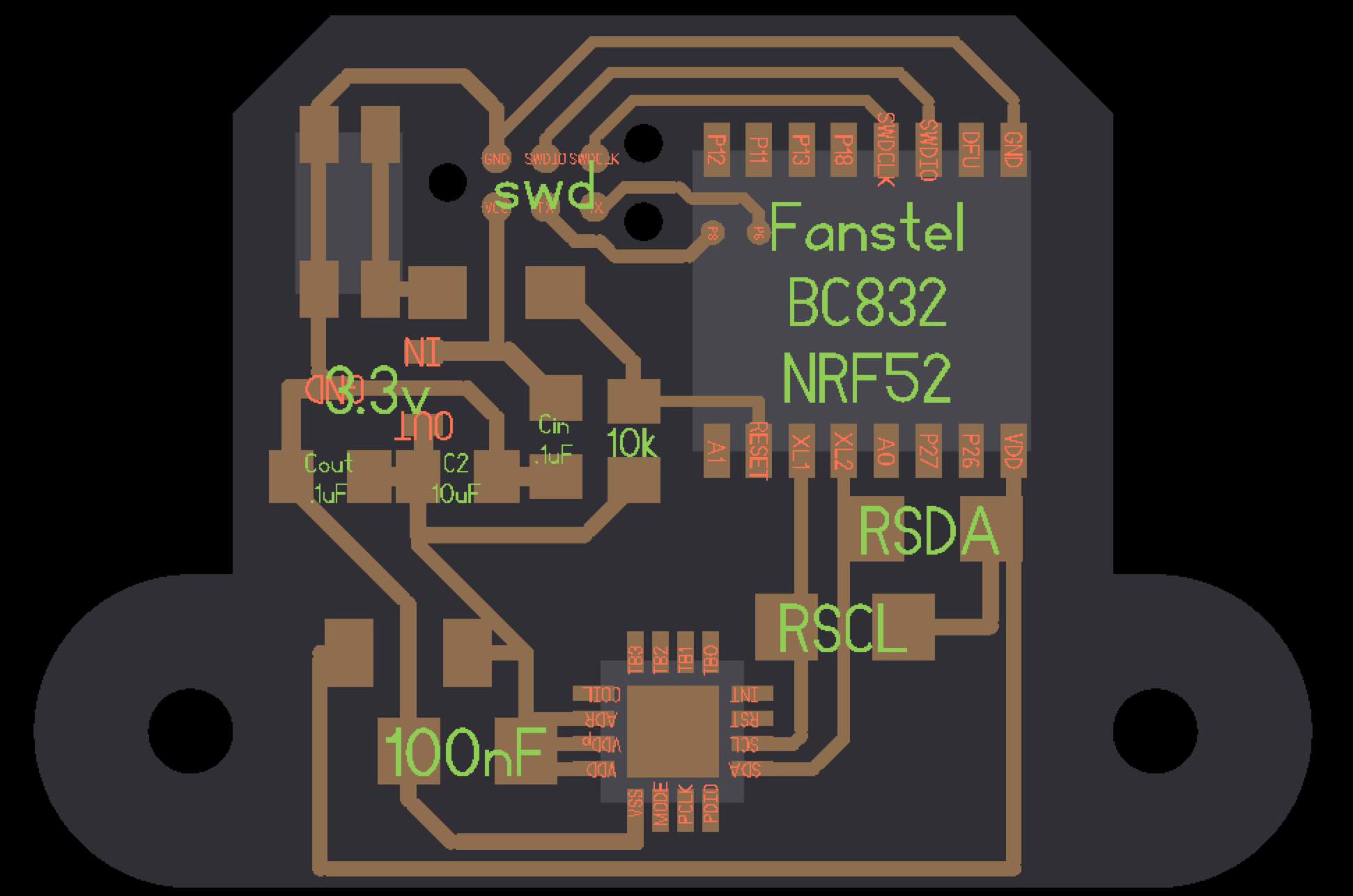

- as5013-test/nrf52-as5013-interior.png 0 additions, 0 deletionsas5013-test/nrf52-as5013-interior.png

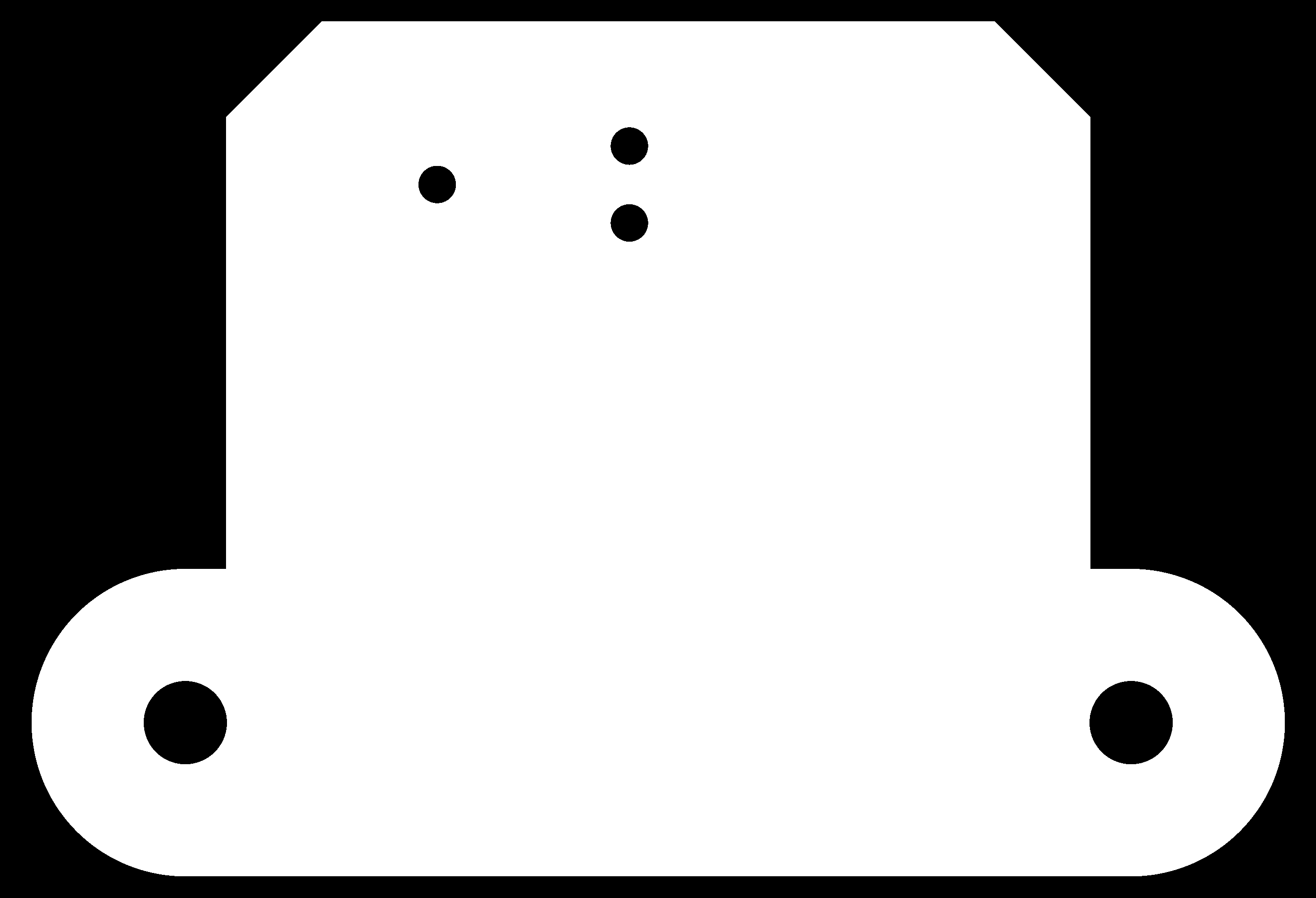

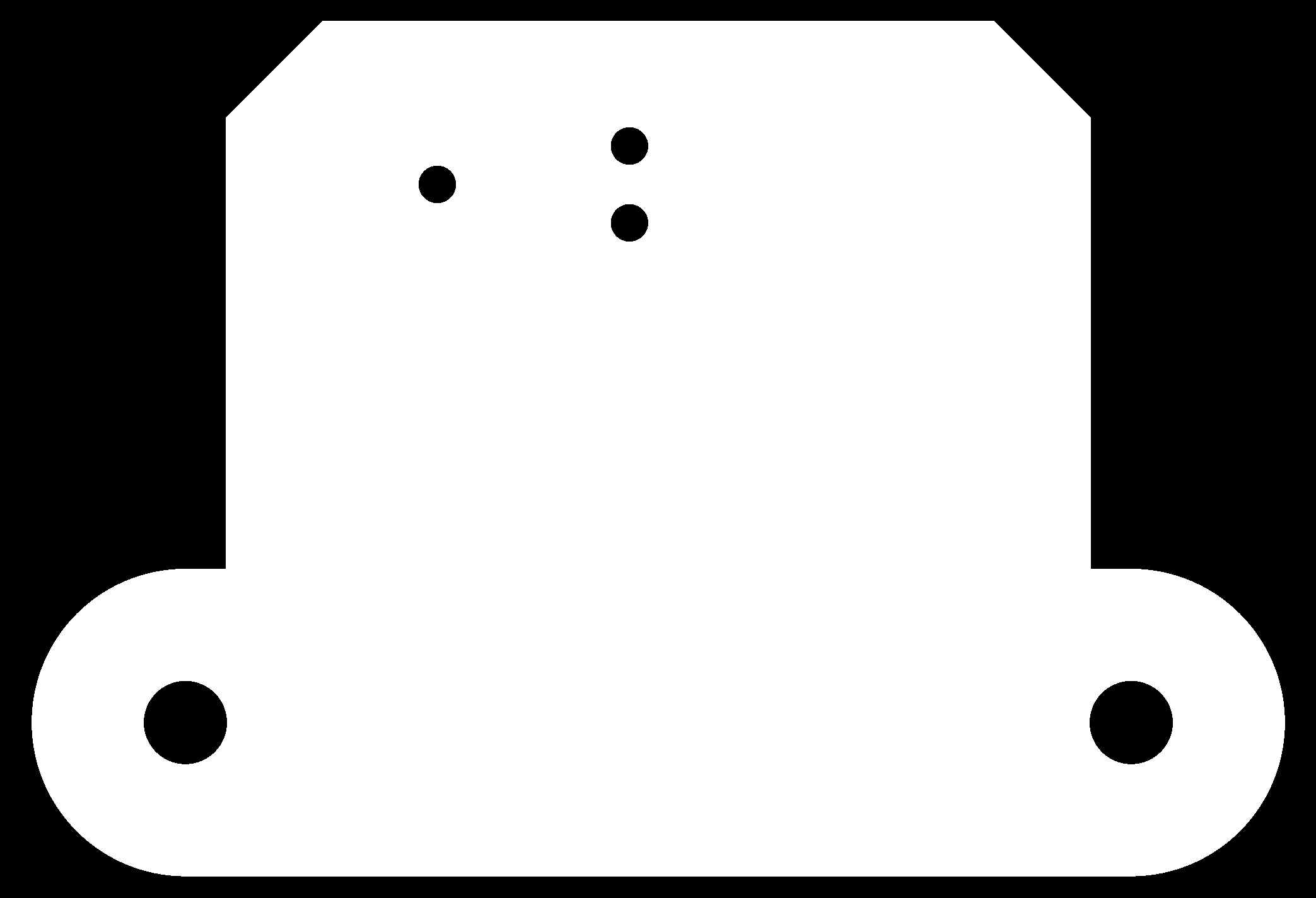

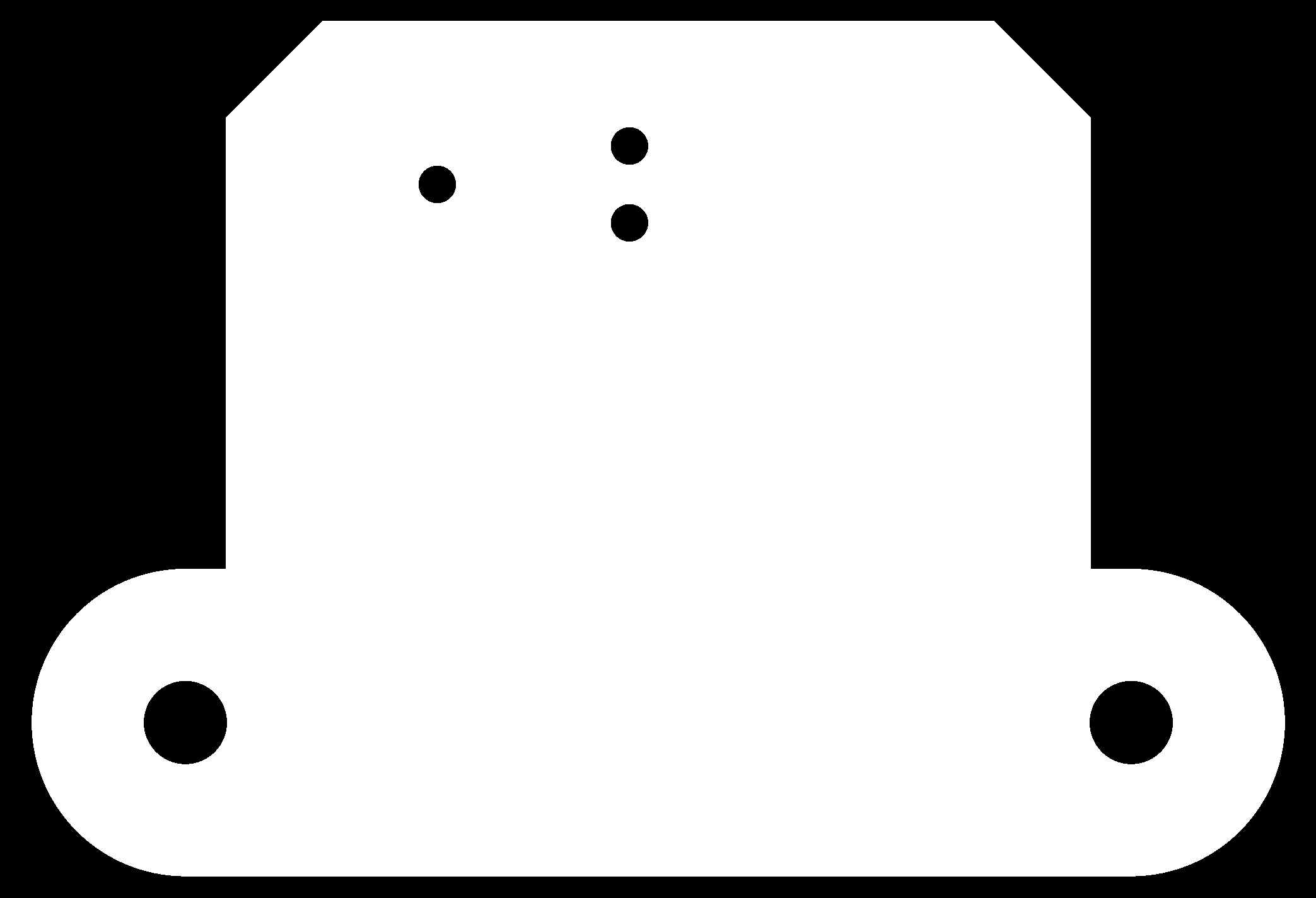

- as5013-test/nrf52-as5013-layout.png 0 additions, 0 deletionsas5013-test/nrf52-as5013-layout.png

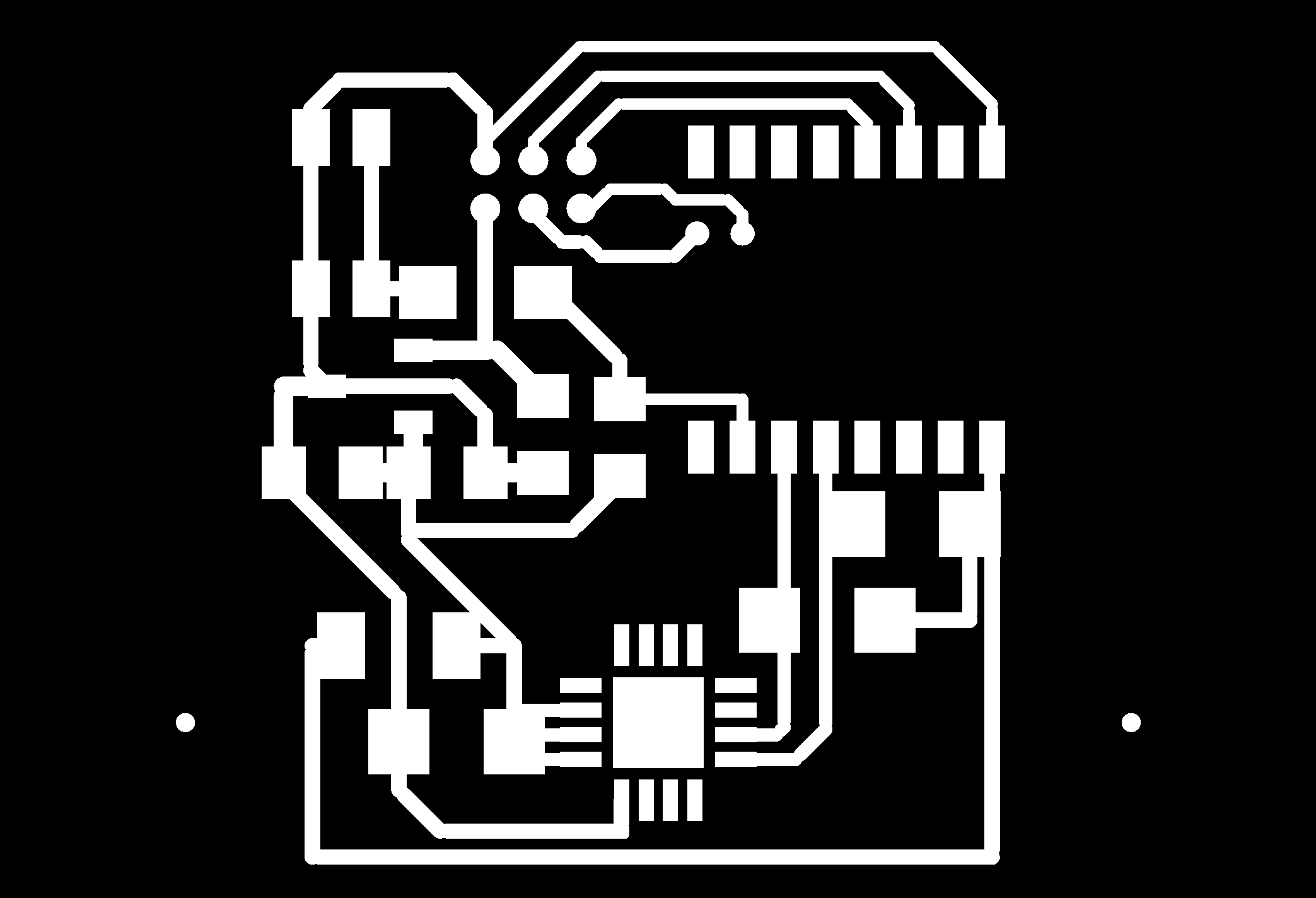

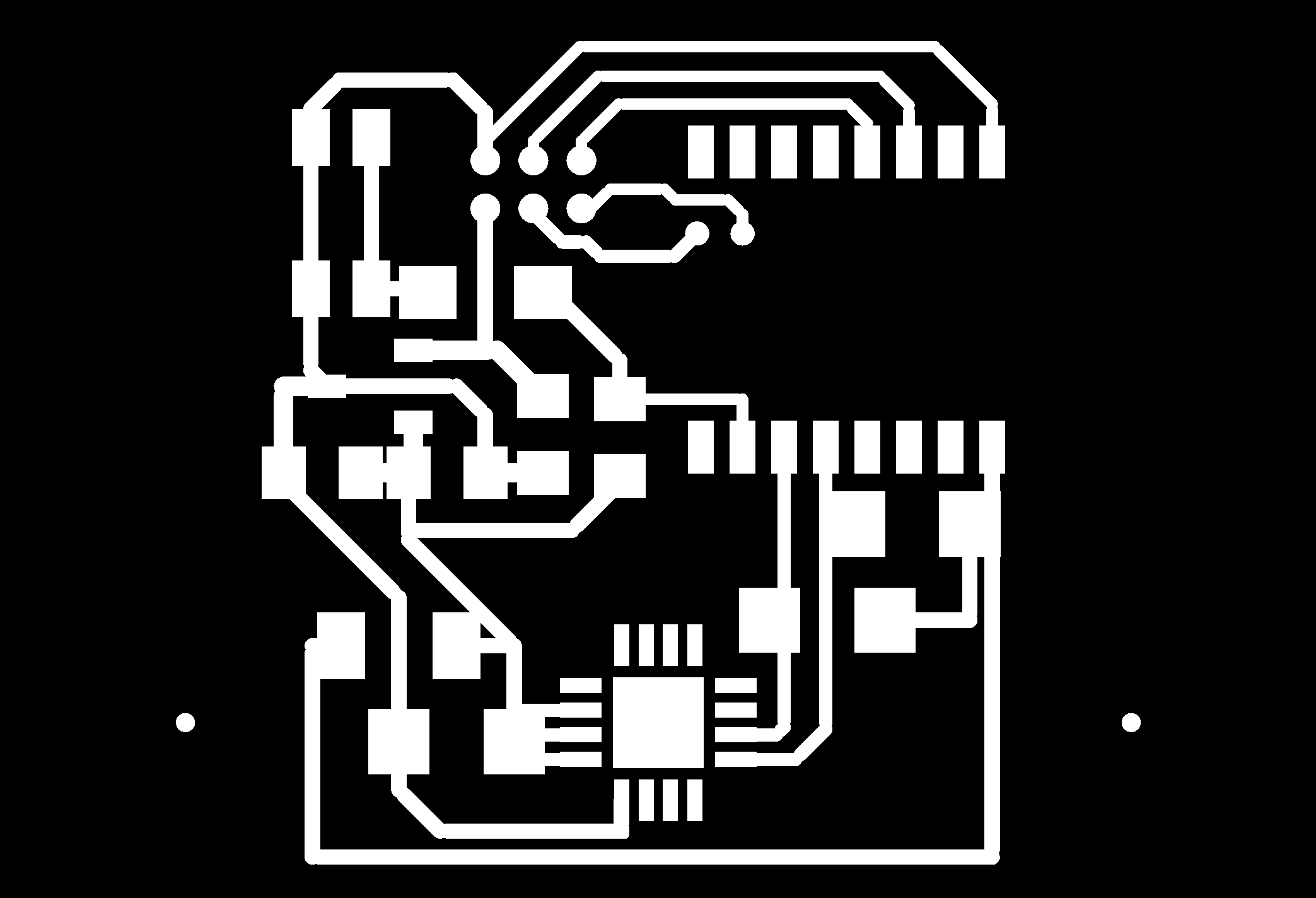

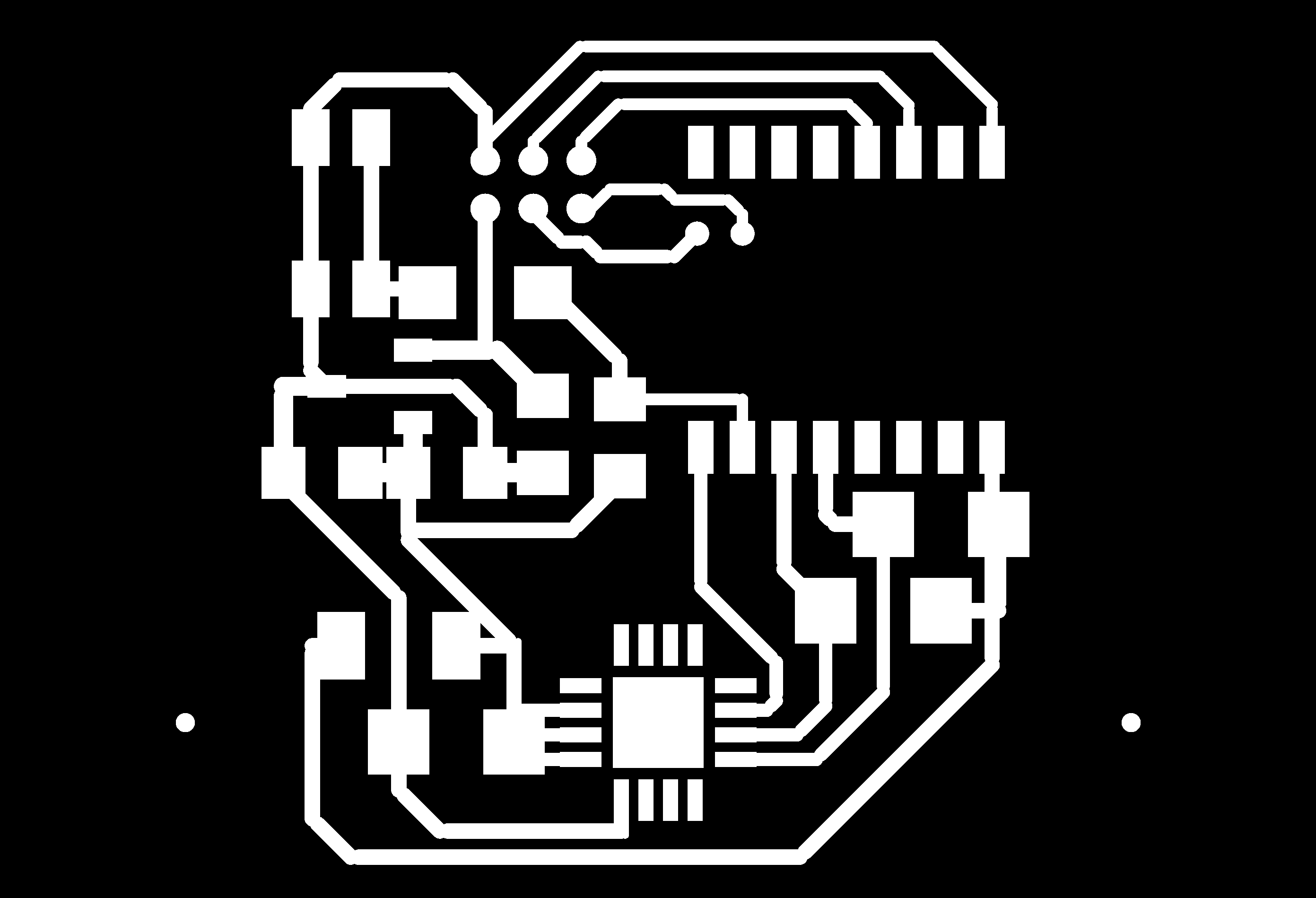

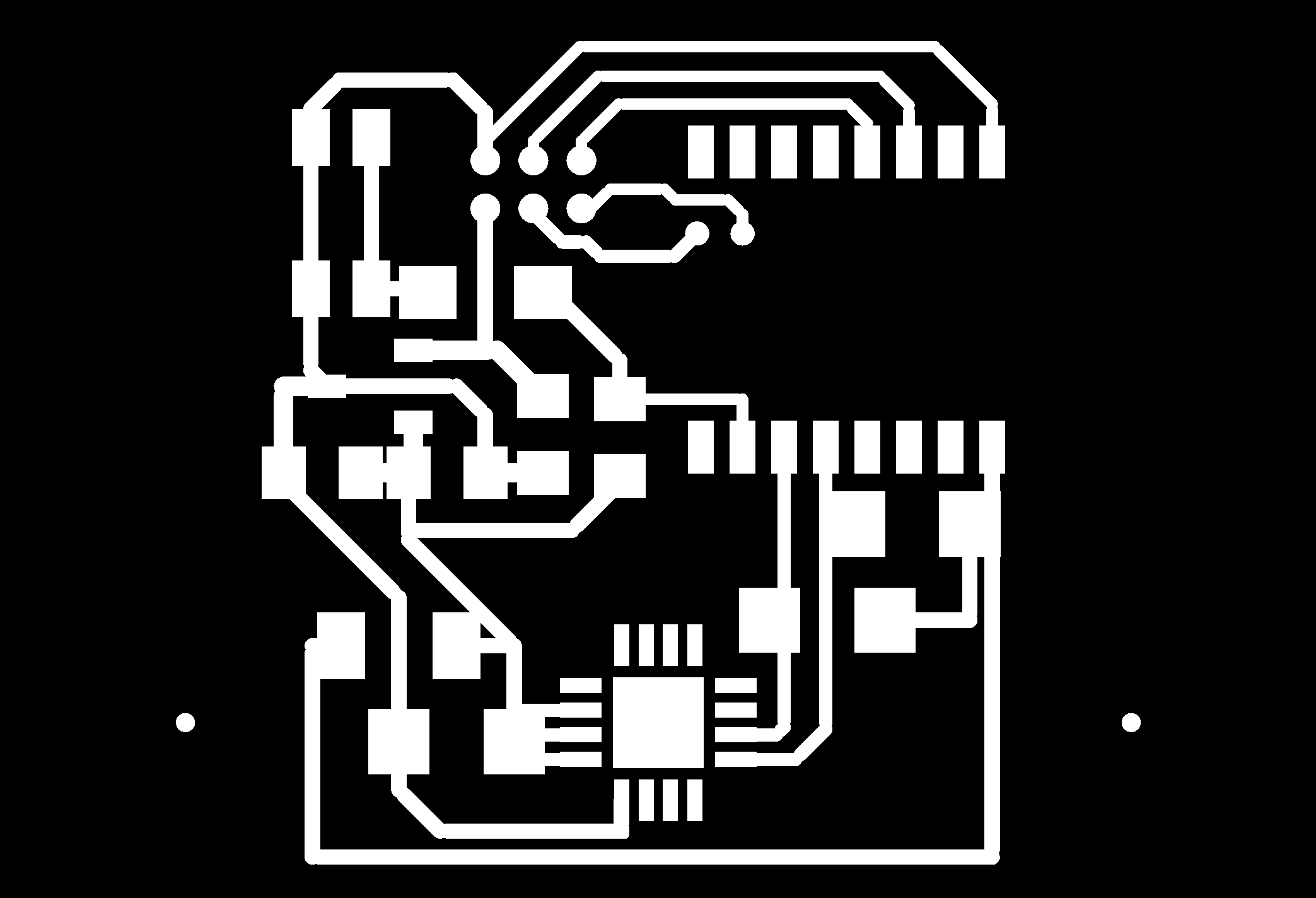

- as5013-test/nrf52-as5013-traces.png 0 additions, 0 deletionsas5013-test/nrf52-as5013-traces.png

- as5013-test/nrf52-as5013.ko 12 additions, 6 deletionsas5013-test/nrf52-as5013.ko

| W: | H:

| W: | H:

| W: | H:

| W: | H:

| W: | H:

| W: | H: